|

ESD 损坏可能是由于电压过高、电流过大或两者兼而有之。高电压可能导致栅极氧化物击穿,而 I 2 R 过大可能导致结故障和金属化迹线熔化。随着制造尺寸不断缩小(英特尔的 Haswell 采用 22nm 工艺),可能导致 ESD 相关故障的电压和电流水平也随之降低。这使得提供哪怕是相对较低水平的片上 ESD 保护也变得困难;因此,重点已转移到单独的 ESD 保护装置上。

改变应用环境会带来问题

笔记本电脑、手机、MP3 播放器、数码相机和其他手持移动设备的普及给高速差分接口(如 USB 3.1、HDMI 2.0、DisplayPort 等)带来了特殊问题。在这些不受控制的环境中,所有者在连接和断开电缆时经常触摸 I/O 连接器引脚;当用户将相机、游戏和其他设备插入其 USB 和视频端口时,设备会不断受到 ESD 压力。

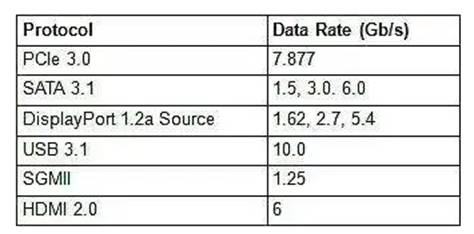

一些常见的高速串行接口

协议 数据速率 (Gb/s) PCIe 3.0 7.877 SATA 3.1 1.5, 3.0. 6.0 DisplayPort 1.2a Source 1.62, 2.7, 5.4 USB 3.1 10.0 SGMII 1.25 HDMI 2.0 6 表 1:一些常见的高速串行接口

IEC 61000-4-2是系统级 ESD 测试的行业标准,旨在复制带电人员在终用户环境中对系统放电的情况。系统级测试的目的是确保成品能够在正常运行中生存,并且通常假设用户在使用产品时不会采取任何 ESD 预防措施。由此产生的静电放电在 30 ns 内可达到 16A(IEC 61000-4-2 4 级,8kV 接触放电)。

ESD防护技术

在高速串行接口中,ESD 保护装置仅仅简单地钳位 ESD 脉冲是不够的:它必须在不损害高速链路的信号完整性的情况下做到这一点。

随着速度的提高,接口在整个信号路径中保持阻抗匹配至关重要。任何阻抗不匹配都会导致线路反射,从而增加抖动并可能损害信号质量,因此高速串行接口要求对信号路径中的任何外部元件有严格的电容限制。

添加所需的 ESD 保护也会增加不必要的额外电容。对于传统的 ESD 设备架构,随着保护级别的提高,设备电容也会增加,迫使设计人员在信号完整性和 ESD 保护之间做出选择。半导体二极管具有许多理想的特性,例如低钳位电压、快速开启时间和更好的可靠性,但直到近,其电容都高于其他架构。

近,制造商推出了专门针对高速应用的电容极低的二极管保护装置。例如,NXP 的PUSB3FR4旨在保护高速接口,例如 10 Gbps 的 SuperSpeed USB 3.1。该设备包括四个 ESD 保护二极管结构,并采用无引线小型 DFN2510A-10(SOT1176-1)塑料封装。

所有信号线均由特殊二极管配置保护,可提供 0.29 pF 的线路电容。二极管采用快速恢复结构,为下游组件提供保护,防止接触 ESD 电压高达 +/-15 kV,超过 IEC 61000-4-2 4 级。

类似的PUSB3FR6具有六个 ESD 器件,为 USB 2.0 和 USB 3.1 的接口组合提供系统级保护,这是新型 USB Type C 连接器的一个特点。

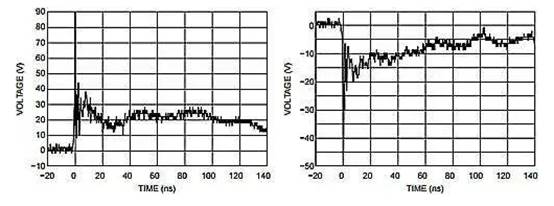

图 1:ESD7008 对 IEC61000-4-2 +/-8kV 接触 ESD 脉冲的钳位响应(来源:ON Semi)

安森美半导体 (ON Semiconductor) 也活跃于该市场:其ESD7008采用 UDFN18 封装,为 4 个差分对 (8 条线) 提供 ESD 保护,对地电容典型值为 0.12pF。

布局建议

PCB 上的许多寄生元件可能会降低系统整体的 ESD 性能,因此需要优化 ESD 保护器件的放置和 PCB 布局,以实现的 ESD 性能。

以下是一些建议:

必须通过缩短返回 GND 过孔的接地路径来尽可能地减少寄生电感。

对称布局也能降低寄生电感。重要的是将连接器连接到ESD设备的一侧,将收发器连接到另一侧。

为了避免 ESD 在 PCB 上传播,ESD 保护装置必须尽可能靠近 ESD 源。

由于 ESD 应力可以在接口电缆的两侧传播,因此需要在电缆的每一端都配备保护装置。

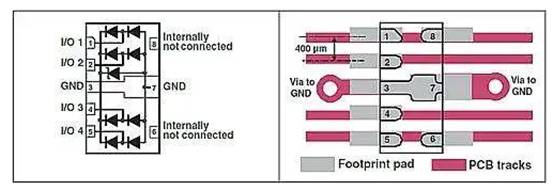

用于高速的 ESD 保护设备使用流通式封装,以方便正确的布局实践。图 2 显示了 ST 的HSP061-4NY8的引脚排列,它为 HDMI、USB 3 和类似接口提供 4 线 ESD 保护。I/O 电容接地为 0.6pF,差分阻抗在 HDMI 规范下为 100 Ω(典型值)。

HSP061-4NY8 引脚分配和流通式封装(来源:ST)

|