|

“电源的完整性是为确认电源来源及目的端的电压和电流是否符合需求。电源完整性在现今的电子产品中相当重要,涉及芯片层面、芯片封装层面、电路板层面及系统层面。

通常,电源完整性是一个整体的概念,"完整性"这个词传达了以下几个方面的含义:

(1) 全面性和全面考虑:完整性意味着考虑到系统中的各个方面,包括电源的设计、电源线路、电源传递、电源管理等。它要求在整个系统中都要有足够的关注,确保电源在所有关键部分都能够正常工作。

(2) 健壮性:完整性还涵盖了系统对于外部扰动和变化的适应能力。一个具有良好电源完整性的系统能够在电压波动、电流变化、电磁干扰等不利因素的影响下,仍能保持其功能的稳定性。

(3) 系统的整体稳定性:这个词语强调了电源系统作为整体的稳定性。这包括了在供电方面的可靠性,以及确保整个系统在正常和异常情况下都能够保持其性能水平。

(4) 功能的保持:完整性还涉及到确保系统的各个功能在各种条件下都能够得以维持。这包括了对电子设备、计算机系统或其他依赖电源的设备而言,电源完整性直接关系到这些设备的可靠性和稳定性。

电源的完整性是为确认电源来源及目的端的电压和电流是否符合需求。电源完整性在现今的电子产品中相当重要,涉及芯片层面、芯片封装层面、电路板层面及系统层面。

电源完整性的结果是否满足要求,是由三个部分综合决定的,即供电模块、传输路径和用电端。我们设计电源电路的时候,对电源的要求是低噪声、低纹波,且输出电压准确、稳定,从而能够尽可能地减少干扰引入。

保证电源完整性,最终是保障用电芯片的噪声裕量[51] [xz2] 。电源噪声的裕量计算的过程如下。

(1)芯片的规格书会给一个规范值,通常是5%;要考虑到稳压芯片直流输出误差,一般是±2.5%,因此电源噪声峰值幅度不超过±2.5%。

(2)如芯片的工作电压范围是3.13~3.47V,稳压芯片标出输出电压是3.3V,安装在电路板后的输出电压是3.36V。容许的电压的变化范围是3.47-3.36=0.11V。稳压芯片输出精度是±1%,即3.36* ±1%=±0.0336V。电源的噪声裕量为0.11-0.0336=0.0764V,即76.4mV。

在计算电源的噪声裕量时,有以下几点需要注意。

(1)稳压芯片的输出电压的精确值是多少。

(2)电源的工作环境的是不是稳压芯片所推荐的环境。

(3)负载情况是怎么样的,这对稳压芯片的输出也有影响。

(4)电源噪声最终会影响到信号质量。而信号上的噪声来源不仅仅是电源噪声,反射、串扰等信号完整性问题也会在信号上叠加。因此不能把所有噪声裕量的要求都是通过提高电源输出的噪声来实现。

(5)不同的电压等级对电源噪声要求也不样,电压越小噪声余量越小。模拟电路对电源要求更高。

最终我们要求在用电器件的接收端接受到良好质量的电源,我们需要整个电源平面的所有的噪声。对于电源的噪声来源:稳压芯片输出的电压不是恒定的,会有一定的纹波;稳压电源无法实时响应负载对于电流需求的快速变化。稳压电源响应的频率一般在200kHz以内,能做正确的响应,超过了这个频率则在电源的输出短引脚处出现电压跌落;负载瞬态电流在电源路径阻抗和地路径阻抗产生压降;外部的干扰。

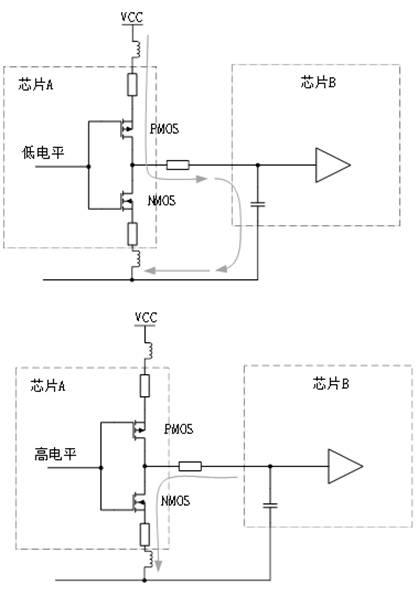

此处提到“负载瞬态电流”,这个问题不是由电源输出端的电源模块或者电源芯片所产生,而是由用电负载自身的负载变化所产生,这个负载变化又是由于大量数字信号在“跳变”所产生。集成电路是由无数的逻辑门电路组成,基本的输出单元我们可以看成是CMOS反相器,如图13.1所示。

图 13.1 CMOS输出的电流示意图

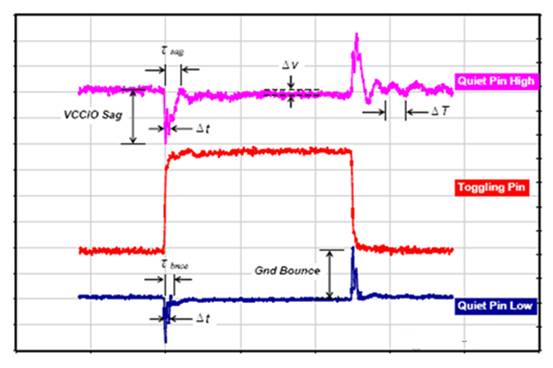

当控制信号是一个低电平的时候,上面PMOS打开,此时输出是高电平。打开的瞬间,VCC通过LVCC和R,对芯片B的输入管脚进行充电。当控制信号是一个高电平的时候,下面的NMOS打开,此时输出的是低电平。打开的瞬间,芯片B的输入管脚储存的电量经过NMOS进行放电。在CMOS反相器输出状态发生变化的时候,流过的电流正是变化的电流。于是,在走线、过孔、平面层和封装(键合引线、引脚)等这些具有电感的链接部件上,便会感应出电压。例如标准的GND地电位应该是0V,但是芯片与地之间的链接部件存在电感,就会感应出电压VGND,那么芯片上的“地”电位就被抬高了,高于0V。如图13.2所示,当CMOS输出信号同时从低电平到高电平切换时,VCC上会观测到一个负电压的噪声,同时也会影响到GND,并有可能引起一个振荡。当输出信号从高电平到低电平切换时,GND上会观测到一个正电压的噪声,同时也会影响到VCC,并有可能引起一个振荡。

图 13.2 CMOS输出变换电压导致的电源和GND的电压变化

一个CMOS会造成这样的干扰,如果有很多CMOS同时工作,用电器件对电源平面和GND地平面造成的干扰会很严重。这就是随着芯片的管脚越来越多,电流越来越大,集成度越来越高造成的我们不得不非常重视电源完整性。

(1)芯片的集成度越来越大,芯片内部晶体管数量也越来越大;晶体管组成内部的门电路 组合逻辑 延迟线 状态机及其它逻辑。

(2)芯片外部电源引脚提供给内部晶体管一个公共的电源节点,当晶体管状态转换时必然引起电源噪声在芯片内部传递。

(3)内部晶体管工作需要内核时钟或是外部时钟同步,但是由于内部延迟及各个晶体管不可能严格同步,造成部分晶体管完成状态转换,另一部分可能处于转换状态,这样一来处于高电平门电路的电源噪声会传到其它门电路的输入部分。

经过上面分析,大家也非常能够理解,为什么要将去耦电容靠近用电器件的电源管脚放置了。

去耦电容(decoupling capacitor)通常被用于电源系统中,目的是提供对电源噪声的短时、高频响应,以维持稳定的电源电压供应给集成电路(IC)或其他用电器件。将去耦电容放置在靠近用电器件的位置有几个关键的理由:

1. 降低电感效应:在电源供电线路中,电源线和地线都有一定的电感。当用电器件瞬时需要大电流时,由于电感的存在,线路中会产生电压降,导致用电器件供电电压下降。通过在用电器件附近放置去耦电容,可以在用电瞬间提供瞬时电流,抵消电感引起的电压降。

2. 降低电源回路的阻抗:去耦电容在高频上具有较低的阻抗。将去耦电容放置在用电器件附近,可以降低电源回路的总阻抗,使电源更容易提供瞬时高频电流需求。

3. 减小电压波动的传播:电源线路上的电压波动会沿着线路传播。通过将去耦电容靠近用电器件,可以减小电压波动的传播距离,确保用电器件获得更稳定的电源电压。

4. 最小化电源噪声对邻近电路的影响:去耦电容可以吸收电源线上的噪声,防止噪声通过电源线传播到邻近的电路。这对于保持邻近电路的稳定性和性能至关重要。

因此,为了最大程度地提高去耦电容的效果,它通常被放置在用电器件附近,以确保对瞬时电流需求的快速响应,并最小化电源系统中的电感和电阻的影响。

小封装和小容值的去耦电容更应该靠近电源管脚的主要原因与这些电容的高频响应和电流传输的特性有关。

高频响应:小封装和小容值的电容通常在高频范围内具有更好的响应特性。由于高频信号的波长短,电容的物理尺寸和电感对其阻抗的影响较小。因此,小型电容更能够提供对高频噪声的有效去耦。

电流传输速度:小封装的电容通常具有较低的等效电感,使其能够更快地传输电流。在高频情况下,电流需要迅速响应用电器件的需求。通过将小电容靠近电源管脚,可以降低电流路径的电感,提高对瞬时电流需求的快速响应能力。

电源噪声的局部处理:小容值的电容主要用于处理局部的、瞬时的高频噪声。通过将这些电容靠近电源管脚,可以在电源引入电路板或芯片的地方提供即时的去耦效果,而不是在较远的位置。这有助于保持用电器件的电源稳定性,减小对整个电路的影响。

采用小封装和小容值的去耦电容靠近电源管脚,有助于优化高频噪声去耦效果,并提供对瞬时电流需求的快速响应。这样的设计有助于维持用电器件的稳定性和性能。

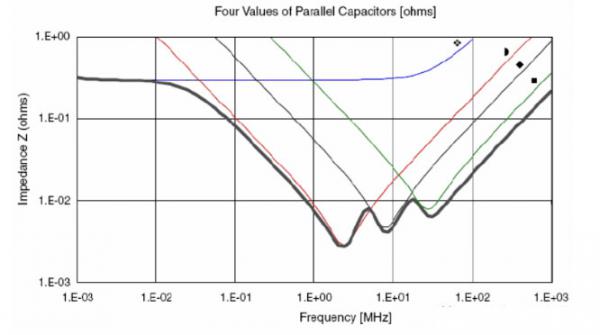

用一个电容组合的例子。这个组合使用的电容为:2个680uf钽电容,7个2.2uf陶瓷电容(0805封装),13个0.22uf陶瓷电容(0603封装),26个0.022uf陶瓷电容(0402)。图中上部平坦的曲线是680uf电容的阻抗曲线,其它三个容值的曲线为为图中三个V字曲线,从左到右2.2uf →0.22uf→ 0.022uf。总的阻抗曲线为底部粗包路线。

这个组合实现了在500K到150M范围内保持阻抗在33毫欧以下,到500M处,阻抗上升到110毫欧,从图中看反谐振点控制的很低。

|