|

基于超级结技术的功率MOSFET已成为高压开关转换器领域的业界规范。它们提供更低的RDS(on),同时具有更少的栅极和和输出电荷,这有助于在任意给定频率下保持更高的效率。在超级结MOSFET出现之前,高压器件的主要设计平台是基于平面技术。但高压下的快速开关会产生AC/DC电源和逆变器方面的挑战。从平面向超级结MOSFET过渡的设计工程师常常为了照顾电磁干扰(EMI)、尖峰电压及噪声考虑而牺牲开关速度。本应用指南将比较两种平台的特征,以便充分理解和使用超级结技术的优点。

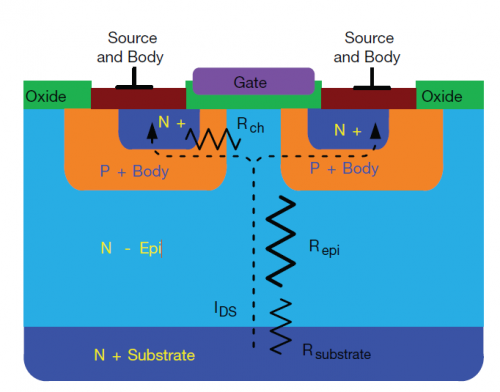

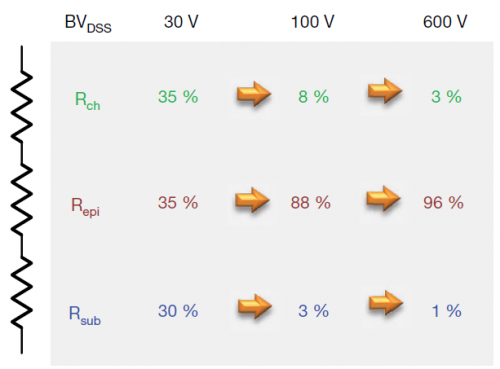

为了理解两种技术的差异,我们需要从基础开始。图1a显示了一种传统平面式高压MOSFET的简单结构。平面式MOSFET通常具有高单位芯片面积漏源导通电阻,并伴随相对更高的漏源电阻。使用高单元密度和大管芯尺寸可实现较低的RDS(on)值。但大单元密度和管芯尺寸还伴随高栅极和输出电荷,这会增加开关损耗和成本。另外还存在对于总硅片电阻能够达到多低的限制。器件的总RDS(on)可表示为通道、epi和衬底三个分量之和:

RDS(on) = Rch + Repi + Rsub

图1a – 传统平面式MOSFET结构

图1b – 平面式MOSFET的电阻性元件

图1b显示平面式MOSFET情况下构成RDS(on) 的各个分量。对于低压MOSFET,三个分量是相似的。但随着额定电压增加,外延层需要更厚和更轻掺杂,以阻断高压。额定电压每增加一倍,维持相同的RDS(on)所需的面积就增加为原来的五倍以上。对于额定电压为600 V的MOSFET,超过95%的电阻来自外延层。显然,要想显著减小RDS(on)的值,就需要找到一种对漂移区进行重掺杂的方法,并大幅减小epi电阻。

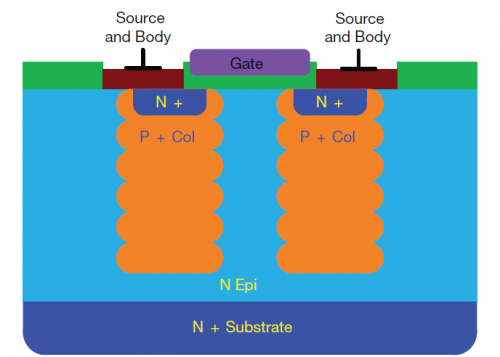

图2 – 超级结MOSFET结构

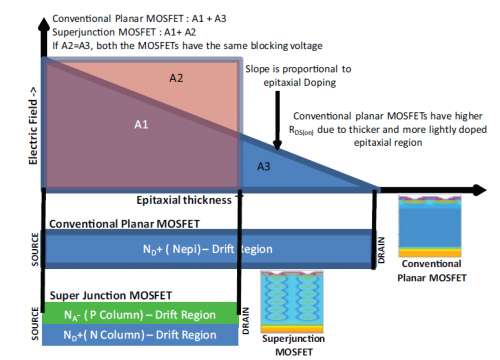

图3 – 平面和超级结MOSFET的电压与导通电阻比较

图2显示了基于电荷平衡概念的超级结MOSFET物理结构。漂移区现在有多个P柱,用于消除处于反向偏压下的周围N区中的电荷。因此,Nepi现在可更薄和重掺杂,因为其组合结构可对施加反向电压提供高很多的电阻。由于N区变得更加重掺杂,所以其单位面积导通电阻减小。

图3比较了两种技术的漂移区电场与epi厚度的关系。在传统平面式MOSFET中,阻断电压由epi厚度和掺杂(ND+)定义,或由掺杂线的斜率定义。如果需要额外阻断电压,不仅epi需要更厚,而且epi掺杂线也需要改变。这导致较高电压MOSFEET的RDS(on)不成比例增加。额定电压每增加一倍,在保持相同管芯尺寸条件下,RDS(on)可能增至原来的三至五倍。

对于给定的阻断电压,超级结MOSFET可使用比传统平面式器件(A1 + A3)更薄的epi(A1 + A2)。N区(ND+)的掺杂被P柱(NA-)的掺杂抵消,导致没有斜率。换言之,因为电荷平衡机制,定义阻断电压的只有epi厚度。因此,超级结结构的导通电阻和击穿电压之间存在线性关系。导通电阻随着击穿电压的增加而线性增加。对于相同的击穿电压和管芯尺寸,超级结MOSFET的导通电阻远小于传统平面式器件。

Vishay提供的超级结器件为E系列高压MOSFET,额定电压范围为500 V - 650 V。这些器件提供从小SMT占位面积(如PowerPAK® SO8和PowerPAK 8 x 8)到标准TO-xxx封装的各种封装选项。典型比导通电阻的变化范围为20 mΩ -cm2至10 mΩ-cm2,具体取决于击穿电压和使用哪一代技术。传统平面式MOSFET的导通电阻x 面积之积有三至五倍高,同样取决于额定电压。例如,TO-220封装600 V器件可实现的最低RDS(on)为275 mΩ,而来自Vishay的同样封装超级结器件可低至50 mΩ。当然,对于每一代新的设计平台,将来会提供具有更低RDS(on)的更好器件。

容值

对超级结器件而言,电阻的减小会带来明显的好处,例如在相同RDS(on)下的更低导通损耗或更小管芯。另外,芯片面积的减小会导致更低的容值以及栅极和输出电荷,这可减小动态损耗。在低压沟槽式或平面式MOSFET中,通常需要考虑以更高容值为让步条件来降低RDS(on)。在超级结技术情况下,让步程度是最小的。电荷平衡机制可同时减小RDS(on)和器件容值,使之成为一种双赢解决方案。

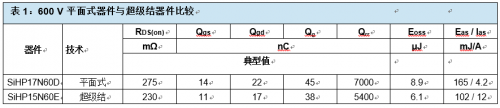

表1比较了具有接近RDS(on)值的两种器件的特征。除Eas和Ias外,超级结器件的每个参数均实现15 % - 25 %的改善。这是因为超级结器件虽然RDS(on)只减小了20%,但其管芯尺寸只有平面式器件的三分之一。更小的尺寸会影响额定电流和功率。大管芯尺寸具有更低的电流密度和更好的散热能力。因此,对于给定的导通电阻,传统平面式MOSFET天生比超级结器件更坚固。但在通常用于高压电源转换器的电流和开关频率下,超级结器件始终具有更低的损耗和更高的效率。

表2显示了500 V器件的比较。SiHG32N50D是一款具有125 mΩ典型RDS(on)额定值的平面式MOSFET。其管芯尺寸大,实际上是适合TO-247封装的最大管芯。这可与采用更小的隔离式细引线TO-220F封装的超级结SiHA25N50E相比,后者提供相同的RDS(on),但除UIS坚固性以外,规格表的每个参数都更好。应当注意的是,Vishay在电感式开关规格降额方面相当保守,对测量故障电流施加100%的降额因子,相当于针对UIS能量Eas的降额因子为4。

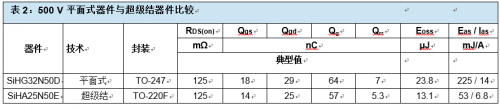

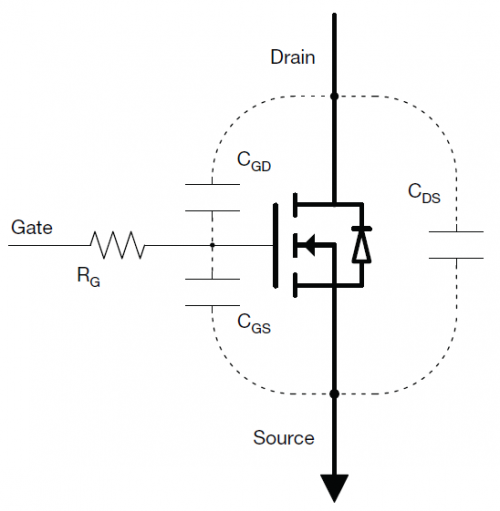

图4定义了提供有电荷规格的器件的容值。对于上文比较的两种600 V器件,容值曲线如图5所示。请注意容值采用对数式标度。

图4 – MOSFET容值定义

图5 – 平面式SiHP17N60D和超级结SiHP15N60E MOSFET的容值比较

栅极电荷考虑事项

在任何开关电路中,栅极驱动设计都要考虑开关速度与噪声这一对矛盾。超级结器件在高压下提供高开关速度,这也需要特别注意驱动设计。设计不佳可能造成电压尖峰、开关不稳定和更高的EMI。与超低容值有关的另一个重要考虑是对耦合和噪声的灵敏性增加,表现为栅源振荡。设计工程师因此不得不通过引入高栅极电阻或低驱动电流来减慢开关速度,最终使系统效率降低。

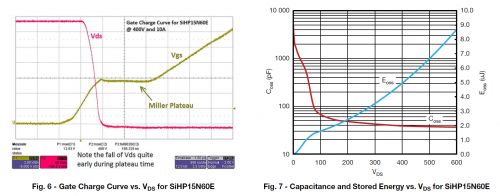

图4和图5显示了来自该应用指南的栅极电荷曲线,它描绘了VDS在栅极放电和充电时的上升和下降。通常,MOSFET的Qgd可用于估计开关期间VDS电压的上升和下降时间。假设用恒定电流源驱动栅极,则tvfall = Qgd / Igon,tvrise = Qgd / Igoff。

这种简单模型不能用于超级结器件,超级结器件的结构和开关行为更为复杂。例如,图6显示了SiHP33N60E的栅极电荷曲线,VDS曲线叠加于其上。与平面式器件相比,超级结MOSFET的一个特征是其容值(VDS的函数)的宽变化范围。在超级结MOSFET中,由于Crss在0 V - 600 V范围内的100:1下降,所以观察到的开关持续时间远小于从产品数据表Qgd值估计得到的数据。虽然没有分析方法可用来预测实际过渡时间(这取决于应用条件),但设计工程师应当知道可使用更低栅极驱动电流来实现优异的开关性能。与平面式MOSFET器件相比,这使超级结器件可使用尺寸更小、成本更低的栅极驱动器。

图6 – SiHP15N60E的栅极电荷与VDS关系曲线

图7 – SiHP15N60E的容值和储存能量与VDS关系曲线

Coss、Co(tr)、Co(er)和Eoss

图5还显示了超级结器件的Coss低近40%,导致更少的储存能量和更快的开关速度,同时实现更低损耗。所有MOSFET的输出容值Coss均表现出与施加电压VDS有关的非线性特征。这种非线性在超级结MOSFET情况下更显著,具有100:1的变化率,电压值的范围为0 V - 600 V。这给需要针对Coss储存电荷和能量有效值的设计工程师带来了挑战。超级结器件产品数据表通常提供针对Coss的两个有效值,定义如下:

Co(tr) - 定义固定电容的值,其在80%额定电压下具有与可变Coss相同的储存电荷。

Co(er) - 定义固定电容的值,其在80%额定电压下具有与可变Coss相同的储存能量。

有几项研究都强调了储存能量Eoss在不同工作条件下对系统效率的影响。由于意识到这一重要性,Vishay已开始提供针对所有高压MOSFET的完整Eoss曲线,一直到图7所示的额定电压。

体二极管特征

由于具有更低的RDS(on)和低容值,超级结MOSFET还是包括ZVS桥在内的所有高频开关应用的器件之选。在ZVS或同步应用中,MOSFET的体二极管不进行硬式整流。二极管电流经过软式整流后流向MOSFET通道,在MOSFET关断时二极管恢复电压阻断功能。但这并不意味着可以想当然地认为,在ZVS桥应用中,在包括瞬态事件在内的所有工作条件下都具有二极管恢复功能。更低的Qrr、短势垒周期和软恢复特征仍然是重要的要求。与平面式器件相比,超级结MOSFET没有Qrr 和trr较低的优点,因而更适合ZVS应用。但体二极管恢复阻断电压的能力被认为非常重要,所以应当进一步改善恢复特征。意识到这一需要,ViShay已推出EF系列超级结MOSFET,在制造中采用额外的工艺,使体二极管的Qrr减小了5-7倍。

结论

超级结结构是高压MOSFET技术的重大发展并具有显著优点,其RDS(on)、栅极容值和输出电荷以及管芯尺寸同时得到降低。为充分利用这些快速和高效器件,设计工程师需要非常注意其系统设计,特别是减小PCB寄生效应。超级结MOSFET具有低很多的栅极电荷,并可用低电流栅极驱动器驱动。其输出容值尽管是高度非线性的,但提供较低的储存能量Eoss及相关输出损耗。Vishay超级结器件提供各种封装、额定电压和体二极管特征,以适合广泛的应用需要。

|