����ʽ������Ӧ��ⰴ����·��һ��Ծ����ر����еĵ�·����˾���ŵ磨ESD�������ṹ��ѡ���������һ���·�Ե��ر���Ҫ��һ����Ҫȷ����ѡ���ESD�����ṹ���㹻�Ŀ�������������һ��������ESD�����ṹ�ֲ���ʹоƬ������ͳɱ�����̫�࣬���ڴ�Ҫ������3��Ӧ���ڵ���ʽ������Ӧ��ⰴ����·�е�ESD�����ṹ����Ҫ��������3�ֽṹ�ĵ�·��ʽ�Ͱ�ͼ���֣����ز�����Ϊ�������ʽ������Ӧ��ⰴ����·�ľ���Ҫ�������3�ֽṹ�����ĸĽ����г�����3�ָĽ������ESD�����ṹ���ص㡢��ռ��оƬ����Լ��������������Խ���ıȽϡ���������������Ľ����3��ESD�����ṹ�ڱ���������оƬ����������Լ��ɿ��Եȷ��涼���˷dz��õ�������

����ʽ������Ӧ��ⰴ����·�ǽ�������ҵ�ڽϸߵļ��ɵ�·��Ʒ�������·ͨ������һ·���߶�·�������ȵĸ�Ӧ����ˣ�ʵ��Ӧ��ʱͨ��������ָ����оƬ����ɵ��ƶ�������������ݶ��ı�Ƶ�ʻ�ռ�ձȣ��Ӷ��ж�������ָ����������ʵ�ְ������ܡ�������֪���������ľ���Я���ߣ������������ָ����оƬʱ���д���������оƬ���ͣ�������DZ�ڵ��ƻ���ѹ�������Լ���ų����Ӷ���оƬ���٣�����Ǿ��籣����electronic staticdischarge��ESD�����⡣ESD�ǽ�����������뵼�壨metal-oxide-semiconductor��MOS�����ɵ�·������Ҫ�Ŀɿ�������֮һ����������Ա��������۵ĵ���ʽ������Ӧ��ⰴ����·��Ϊ�˱�֤�߿ɿ��ԣ������·��ESD��������ͨ��Ҫ��ﵽ8000 V������Ҫ�ﵽ10 000 V����˱���ͨ���ڵ�·�м�����Ч��ESD�����ṹ�����������Ҫ���⣬���ֱ����ṹ�ֲ���ռ��̫���оƬ�����������������оƬ�ɱ����Ӷ�����оƬ���ƹ�Ӧ�á�������ѡ����ʵ�ESD�����ṹ�����ܱ�����һ�ഥ����Ӧ��������·���ֲ�����̫������оƬ�ɱ��������·�����������Ҫ�����⡣

���Ľ�����3��Ӧ���ڱ����������ĵ���ʽ������Ӧ��ⰴ����·�е�ESD�����ṹ����3�ֱ����ṹ�ڴ�ͳESD�ṹ�����Ͻ�ϵ���ʽ������Ӧ��ⰴ����·�ľ����ص����ȫ��Ľ����Դﵽ������·�Ҿ����ٵ�����оƬ�����Ҫ����Щ�ṹҲ�������������Ƶĵ�·��ϣ���ܹ��������¼��ɵ�·��ƵĹ���ʦ�ڿ���ESD����ʱ�ṩһЩ�ο���ơ�

1��3��ESD�����ṹ

1.1�������ܼӵ���ESD�����ṹ

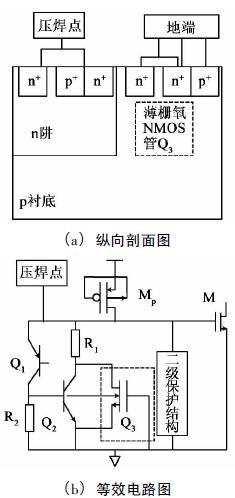

ͼ1��a����MOS���ɵ�·�������һ��ESD�����ṹ����Ҫ�ڵ�·��ÿһ��ѹ���㶼����ýṹ������ͼ�е�Mp��Mn����MOS�ܡ����ֽṹ������ѹ����ֱ��������դ����Դ���̽ӵ�PMOS��Mp�Լ�դ����Դ���̽ӵ�NMOS��Mn.����Mp��Mn���������ӿ��Ե�Ч������������D1��D2.ʵ��Ӧ��ʱ��ѹ�����ϻ�����ϴ�ľ��磬���ݾ����ԭ��������ϴ�ľ��������Mp��Mn�������ӱ�ѩ��������ͨ������ͼ1��a���е�ESD�����ṹ��������绹û�е���Mp��Mn֮ǰ������������������D1��D2����������γɵ���Դ�͵صĵ���ͨ·���Ѵ����й�ŵ����������R���������á���������ʩ�����˱���Mp��Mn�����á�����ESD�����ṹ��ESD��������ͨ����2000��3000V.Ϊ�˽�һ�����ESD�����������ڵ���ʽ������Ӧ��ⰴ����·�ж����ֽṹ���иĽ�����ͼ1��b����ʾ��ͼ1��b����ʾ��һ�����NMOS�ܵ����������ܼӵ��������ESD�����ṹ�����PMOS�ܵı����ṹ������ơ�ÿһ����ԭ����ͼ1��a�����ƣ������ֽṹ�ܹ�������������Ͷ���������������ͷ�ѹ�����ṩ���й��ͨ·���Ӷ���й�Ŵ���������ESD������������ͼ1��b���е�MOS��MnΪ����˵�����ָĽ���ESD�����ṹ�ĵ�·�ṹ����Ӧ�����ѡ��Mn��դ������ѹ��12.5V������ESD����ԭ���������༶��������֮������Mnդ���ĵ�ѹ��С��������ӵ�դ������ѹ��������·�����������ã�ͨ�����㣬�������������ܼӵ�������ṹ���Դﵽ����Mn��Ŀ�ģ�����ÿһ����������ֵΪ100������D1��D2��D3 3��������Ҳ���Բ���ͼ1��a������ʾ��դ����Դ���̽ӵ�MOS�ܡ�

ͼ1�����ܼӵ���ESD�����ṹ

1.2���ɿع���������ESD�����ṹ

ͼ2��a���ǿɿع���������silicon controlledrectifiers��SCR��ESD�����ṹ����������ͼ��ͼ2��b�������ֽṹ�ĵ�Ч��·ͼ��

ͼ2��b����Mp��һ��դ����Դ���̽ӵ�PMOS�ܣ���ESD�������ã�Q1��һ��pnp�������ܣ��䷢��������n���ڵ�p+��ɢ�����ɣ�n�������Ļ�����p�ĵ���Ϊ����������һ��Q2��npn�������ܣ������n+���䷢������p�ĵ������Ļ�����n���Ǽ����������������������һ����֮Ϊ�ɿع���������4��뵼����������4��������p+��ɢ����n�塢p�ĵ�n+��ɢ��������pnpn�ṹ����npn��pnp֮������������ṩ�����õ�ESDй��ͨ·�����зdz����Ե�ESD�������ܡ������оƬ��ÿһ��ѹ�����϶���������һ���ṹ����������С�IJ���������ṩ��ߵ�ESD����������ͼ2��b����R1��n��Ӵ����裬R2��p�ĵӴ����衣

�ݰ뵼������ԭ����������4��ṹ��ΪESD����������˵������ʼ��ͨ��ѹ��Ч��MOS������n����p�ĵ�֮��Ļ�����ѹ������n����нϵ͵IJ���Ũ�ȣ������ɰ뵼�幤���������ģ��������p�ĵ�֮��Ļ�����ѹ�ߴ�30��50V����˸ߵĻ�����ѹʹSCR�ṹ��ESD�����������Ҫ�ټ��϶���Ķ��������ṹ����ͼ2��b�����Ѿ���ע������������Ϊͼ2��b������Ҫ������MOS��M��դ������ѹֻ��12.5V���ң���SCRҪ��30V���ϲŵ�ͨ����ESD��ѹ��δ����30V֮ǰ�����SCR�ṹ�ǹرյģ���ʱSCR������Ҫ������M����ͱ�ESD��ѹ�ƻ��ˣ���˱��������������ṹ������������������ṹ�����䱻ESD�ƻ�֮ǰ��SCR�ṹ�ܹ���������ͨ���Ӷ�й��ESD������ֻҪSCR�ṹһ��ͨ����͵ı��ֵ�ѹ���ǯ��סESD��ѹ�ںܵ͵�ֵ��������SCR�ṹ������Ч�ر���M�ܡ������ֶ������ӵĶ��������ṹ��Ȼ�����оƬ��������ӣ�����оƬ�ɱ���������

ͼ2 SCR ESD�����ṹ��������ͼ�����Ч��·ͼ

Ϊ���������⣬�ڵ���ʽ������Ӧ��ⰴ����·�в�����һ�ָĽ���SCR ESD�����ṹ���ڸýṹ������һ��ͼ2��b�����߿�����ʾ�ı�դ��NMOS��Q3.���ݾ����ԭ����������ѹ��դ����ֱ����صġ����NMOS���ԙM��ķ�ʽ��n����p�ĵĽ����ϣ�����ʹSCR�ṹ����ʼ��ͨ��ѹ�½���10��15V�����ʹSCR�ṹ����Ҫ����Ķ��������ṹ�������Ч�ر�����·�ڲ�M�ܣ��Ӷ���С��оƬ�����SCR�ṹ�ĵ�ͨ�����������£�����Ƕ�ı�դNMOS��Q3������������ʱ��������������դ������p�ĵף�������������n������p�ĵף�Ҳ���������SCR�ṹ�ĵ�ͨ��Ϊ�˷�ֹSCR�ṹ����ͨMOS���������������»ᱻ��ͨ������Ƕ�ı�դNMOS��Q3��դ������Ҫ���ӵ��أ��Ա��ָ�NMOS�ܹرգ���ͼ2��b����ʾ��

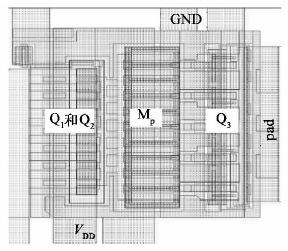

ͼ3��ʾ�˸Ľ���SCR ESD�����ṹ�İ�ͼ��������ΪESD����������Q1��Q2�Ϳ�����Ϊ180/1��PMOS��Mp�����о�����ΪESD�������������ı�դ��Q3.ͼ��VDD�ǹ������ӵĵ�Դ�ˣ�GND�ǹ������ӵĵضˡ�

ͼ3�Ľ���SCR ESD�����ṹ��ͼ

1.3��ȫоƬESD�����ṹ

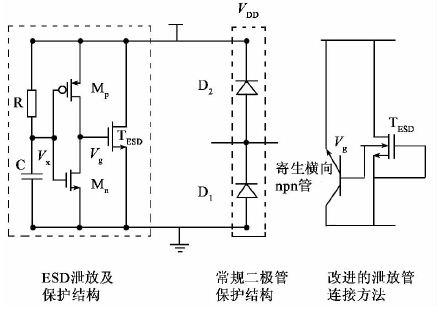

ͼ4��ʾ��һ��ȫоƬ��ESD������·�ṹ�����ֱ����ṹ��ESDй�ż������ṹ�ͳ�������ܱ����ṹ��������ɡ�����ESDй�ż������ṹ��RC���硢Mp��Mn���������ƹ��Լ�ESD����й�Ź�TESD����ɡ��ⲿ��ԭ���������£�ESD�Ե�·��������Ҫ�ǵ�·��pn���������ɵIJ���������µ�·©�硣��VDD�����ϳ���ESD��ѹʱ��ͼ��Vx��ij�ʼ��ѹΪ�㣬���ڵ��ݵġ����ԡ��������˵�ѹ����ͻ�䣬���Mp�ܵ�ͨ��Vg�˵�ѹ������ESD��ѹ������TESD�ܵ�ͨ��ΪESD�����ṩ��һ�����ص�й��ͨ·��TESD�ı�դ��������ͼ��Vg��ĵ�ѹ��������̫�ߣ���������դ���Ӷ������������RC������̧��Vx�˵�ѹ������Vg���ߣ�RC���ʱ��һ��Ҫ�ܹ���֤ESD��й����Źض�Mn�ܣ�һ��Ҫ����200ns���ң�Ҫ��TESD�ܵ�����ܹ����ش���������Ҫ����㹻��դ�����ȡ���������£�TESD�ܵ�դѹΪ0V����ʵ�ǹرյģ���˲�Ӱ��оƬ������������

ͼ4ȫоƬESD������·�ṹ

����ȫоƬ��ESD�����ṹ�ܹ��ܺõ���ߵ�·��ESD���������������뵼�幤�յ������Σ�Ϊ�˷�ֹ��������ЧӦ��������MOS��Դ©�˲���dz���ӣ� lightly doped drain��LDD���ṹ��ͼ4�е�TESD�ܾͲ�����LDD�ṹ����TESD�ܵ�ͨй��ESD����ʱ���������������ӵı���ͨ�������������dz��dz���Ӵ����������Ӷ�����������ȫоƬESD�����ṹ�ķ���������

�ڵ���ʽ������Ӧ��ⰴ����·�в�����һ�ָĽ���ȫоƬESD�����ṹ���Ľ�����ESD����й�Ź�TESD�����ӷ�ʽ����ͼ4��ʾ�������Ľ���TESD�ܵ�դ�ӵأ���Vg�����TESD�ܵijĵף����������ṹ�Ͳ������ֲ��䡣��ͨ����ȫоƬESD�����ṹ��ȣ����ָĽ���ȫоƬESD�����ṹ�����˼����ĺ���npn�ܣ���ͼ4��ʾ��

�����ָĽ���ȫоƬESD�ṹ�У���VDD�����ϳ���ESD��ѹʱ��������Vg��ѹ�仯�����ڵ�ѹ�Ĵ��ڣ�������ĵ��ϵ��ӵ�Ǩ�ƶ��γɵ��������������ĵ�����̧����npn�ܵĻ�����ѹ�����ջᴥ�����npn�ܵĵ�ͨ����ʱESD������ͨ��npn���ڳĵ���������������MOS�ܱ���������TESD�ܲ�û�п���������������ĺ���npn����й��ESD��������LDD�ṹ�����ܵ�ESD���������������ܴ��������ֱ�����·ESD����������

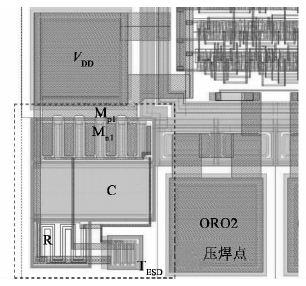

ͼ5�����߿������ָĽ���ȫоƬESD�����ṹ�İ�ͼ����ͼ��ʾ�������ƹ�Mp��Mn��RC�����Լ�����Ҫ�ı�դ��TESD��λ�ã����е��������µ���������ESD̽��������ͼ5���Կ�����һ��ȫоƬ��ESD�����ṹ��ռ��оƬ���ֻ��һ��ѹ���������Դ�Ҳ����˵��ijһ��оƬ�в�������ȫоƬ��ESD�����ṹ���������оƬ���������̫�࣬�����Դ����߸�оƬ��ESD����������

ͼ5ȫоƬESD�����ṹ�İ�ͼ

2��3��ESD�����ṹ�ȽϺͲ��Խ��

2.1��3�ֽṹ�ڲ�ͬESD����ģʽ�µ������ԱȽ�

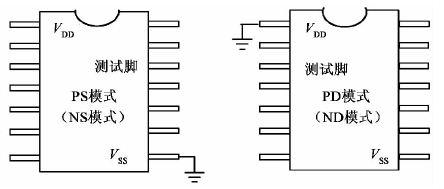

����оƬ��ÿ���˿ڣ�����4��ESD�IJ���ģʽ����ԡ�VDD�͡�VSSģʽ���в��ԣ��ֱ��Ϊ���в��ԽŶ�+VDD��PSģʽ�����в��ԽŶԣ�VDD��NSģʽ�����в��ԽŶ�+VSS��PDģʽ�����в��ԽŶԣ�VSS��NDģʽ����ͼ6��ʾ���������ijһ�����Խţ�ʩ�����Ļ�ESD��ѹ�������Ķ˿�ȫ�����գ�ֻ�е�4��ģʽȫ���ɹ�ͨ��ijһ��ѹ����4000V�����ԣ�������Ϊ�˶˿ڵ�ESD���������ﵽ��4000V.

ͼ6 4��ESD����ģʽ

���ڶ����ܼӵ����ESD�����ṹ�����ж�����ͨ������դ���ӵص�NMOS�ܺ�դ���ӵ�Դ��PMOS����ʵ�֡���������ESD�����ṹ�ĵ�·һ���NS��PD���ֲ���ģʽ��ESD���������Ƚϸߣ������ND��PS���ֲ���ģʽ��ESD����������Ҫ�����ࡣ������Ϊ��NS����ģʽ��ijһ�����Խ��Ͻ��븺��ESD��ѹ��NMOS�ܼ����Ķ���������ͨ��ͬ��PDģʽ��VDD�˽ӵأ�ijһ�����Խ��Ͻ�����ESD��ѹ��PMOS�����Ķ���������ͨ����ͼ1��b����ʾ����ND��PSģʽ�£�������������Ҫ���������й��ESD����������ijһ�ض��������ܳ��ܵ�ESD�����ǹ̶��ģ������ܵ�����ͨ��ѹΪ0.7V���ң�ԶС���䷴�������ѹ����˶���������ͨʱ�ܳ��ܵ�ESDй�ŵ���ҲԶԶ�����䷴�����ʱ����ESD��ѹԶ���ڷ������ʱ��ESD��ѹ�����ND��PSģʽ��ESD���������������ֱ����ṹ��ȱ�㡣

ͬ�����ɿع�������ESD�����ṹҲ��ͬ�������⡣ȫоƬESD������·���ÿ��Խ��������⣬�Ӷ���ʾ�����ֽṹ��ǰ���ֽṹ����Խ�ԡ�ԭ���������£���PSģʽΪ������Դ�����գ��ؽŽӵ͵�ƽ����û��ȫоƬESD������·ʱ��D1���������ܽ��������й��ESD������������ESD��ѹ���ͨ��D2�䵽VDD�����ϣ���ͼ4��ʾ����ͨ��ESD������·й�ŵ��ء�����ESDй¶��ʽ������D1�����������ij��֣�ͬ��NDģʽҲ����������˼·������

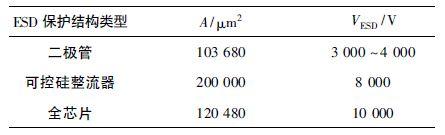

2.2��3�ֽṹ��ռ�õ�оƬ����Լ�ESD��ѹ���Խ���Ƚ�

������3�ֽṹӦ�õ�����ʽ������Ӧ��������·������У�оƬ���õ���0.35��m MOS���գ�����10��ѹ���㡣3�ֽṹ��ռ�õ�оƬ������1��ʾ������AΪESD�ṹ��ռ�õ�оƬ�����VESDΪESD��ѹ���Եĵ�ѹ��

��1 3��ESD�����ṹ��ռ�õ�оƬ�����ʵ��ESD��ѹ���Խ��

�Բ���3�ָĽ���ESD�����ṹ��оƬ����ESD��ѹ���ԣ�������1��ʾ���ӱ�1�ȽϽ�����Կ�����ȫоƬESD�����ṹ�ȶ�����ESD�����ṹ��ռ�õ�оƬ���������16800��m2��������ӵı���Ϊ16%����ESD�������������2���ࣻ�����ɿع�������ESD�����ṹ��ȣ�ȫоƬESD�����ṹ��ռ��оƬ���ֻ�пɿع�������ESD�����ṹ��60%����ESD��������ȴ�����2000V������ȫоƬESD�����ṹ������õ�ESD����������

2.3��3�ֽṹ��ESD�����������Խ��

��ESDģ��֮һ������ģ��ҵ���Ա�HBMMIL��STD��883F3.15.7�Բ�������3�ָĽ����ESD�����ṹ�ĵ���ʽ������Ӧ��ⰴ����·����ESD�����������ԡ���PSģʽΪ������˵�����Է������£�ÿ�ֵ�·��3����Ʒ����3����Ʒ���ȱ���ͨ�����ܵIJ��ԣ���Դ�����գ��ؽŽӵ͵�ƽ���������йܽ�Ҳ�������գ���ijһ�����Խ���ʩ������ѹ����Чʵ�ʵ�·ʹ��ʱ�����ܵ�����ESD��ѹ����ʼ��ѹΪ500V���Ժ�ÿ��һ�β��Ե�ѹ��������500V��Ҳ����˵������ѹΪ500V��Ȼ���ظò��Խ���ʩ��ESD��ѹǰ��ĵ�������ѹ���ߣ�ͨ�����ð����߷����ж�ʩ��ESD��ѹǰ����Խŵĵ�������ѹ���ߵı仯�����������С��15%�ж�Ϊʩ��ESD��ѹǰ��ĵ�������ѹ����û�б仯���ùܽŻ����Գ��ܸ��ߵ�ESD��ѹ�������������ӵ�ѹ��ֱ������15%�����Χ������ӵ�4500V��������߳�����15%���ͱ����ò��Թܽ��Ѿ�������ESD���ܷ�Χ������ʱ���ӵ�ESD��ѹ4500V��ǰһ����Ҳ����˵4000V���Ǹò��Խ����ܳ��ܵ����ESD��ѹ���ٶԸò��ԽŽ���NS��PD��ND������3��ģʽ�IJ��ԣ����4��ģʽ����ͨ��4000V�����Ҿ���ESD������·�Ĺ���û�иı䣬��Ҫ3����Ʒ�����ظ������飬��ű�ʾ����ܽŵ�ESD��ѹΪ4000V.

ͨ��ESDˮƽ��Ϊ������һ��Ϊ0��1999V������Ϊ2000��3999V������Ϊ4000��8000V.����һЩ�����Ӧ�ã�ESD��ѹҪ��10000V���Ǿ����������Ļ����ϼ�����������ESD��ѹ��ֱ�����ӵ�ѹ����10000V�����Ҳ��Խŵĵ�������ѹ����û�б仯��������оƬ��ESD��ѹ���Ըߴ�10000V.

3������

����ʽ������Ӧ��ⰴ����·Ҫ������ر�ߵ�ESD������������˱��������Ч��ESD�����ṹ�������о��˶����ܼӵ��衢�ɿع���������ȫоƬ��3��ESD�����ṹ�����ص���Ե���ʽ������Ӧ��ⰴ����·�Ľṹ�����ص㣬����˶���3�ֱ����ṹ�ĸĽ���ʩ��������������Ľ����3��ESD�����ṹ�ڱ���������оƬ������������Լ��ɿ��Եȷ��涼���˷dz��õ�����������ȫоƬESD�����ṹռ�õ�оƬ�����С�����������ESD����ģʽ������õ�ESD�������������ֽṹ�����ƹ㵽�������ͼ��ɵ�·��ESD�����ṹ����С�

|